# Hardware Efficient PDE Solvers in Quantized Image Processing

Vom Fachbereich Mathematik der Universität Duisburg-Essen (Campus Duisburg)

zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation von

> Robert Strzodka aus Tarnowitz

Referent: Prof. Dr. Martin Rumpf Korreferent: Prof. Dr. Thomas Ertl Datum der Einreichung: 30 Sep 2004 Tag der mündlichen Prüfung: 20 Dez 2004

# Contents

| At  | ostra                                         | ct                                                        | v                                                               |

|-----|-----------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|

| 1   | 1.1<br>1.2<br>1.3                             | Oduction         Motivation                               | <b>1</b><br>2<br>5<br>8<br>11                                   |

| 2   | PDE                                           | Solvers in Quantized Image Processing                     | 13                                                              |

| 3   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Continuous PDE Based Image Processing                     | 15<br>24<br>43<br>55<br>59<br>63<br>67<br><b>69</b><br>71<br>84 |

|     | 3.2<br>3.3<br>3.4                             | Hardware Architectures                                    | 97<br>105                                                       |

| 4   | <b>Hard</b><br>4.1<br>4.2<br>4.3<br>4.4       | dware Efficient Implementations         Graphics Hardware | <b>107</b><br>110<br>156<br>165<br>180                          |

| Bi  | bliog                                         | raphy                                                     | 187                                                             |

| Ac  | rony                                          | ms                                                        | 201                                                             |

| Inc | dex                                           |                                                           | 205                                                             |

# Abstract

Performance and accuracy of scientific computations are competing aspects. A close interplay between the design of computational schemes and their implementation can improve both aspects by making better use of the available resources. The thesis describes the design of robust schemes under strong quantization and their hardware efficient implementation on data-stream-based architectures for PDE based image processing.

The strong quantization improves execution time, but renders traditional error estimates useless. The precision of the number formats is too small to control the quantitative error in iterative schemes. Instead, quantized schemes which preserve the qualitative behavior of the continuous models are constructed. In particular for the solution of the quantized anisotropic diffusion model one can derive a quantized scale-space with almost identical properties to the continuous one. Thus the image evolution is accurately reconstructed despite the inability to control the error in the long run, which is difficult even for high precision computations.

All memory intensive algorithms are, nowadays, burdened with the memory gap problem which degrades performance enormously. The instruction-stream-based computing paradigm reenforces this problem, whereas architectures subscribing to data-stream-based computing offer more possibilities to bridge the gap between memory and logic performance. Also more parallelism is available in these devices. Three architectures of this type are covered: graphics hardware, reconfigurable logic and reconfigurable computing devices. They allow to exploit the parallelism inherent in image processing applications and apply a memory efficient usage. Their pros and cons and future development are discussed.

The combination of robust quantized schemes and hardware efficient implementations deliver an accurate reproduction of the continuous evolution and significant performance gains over standard software solutions. The applied devices are available on affordable AGP/PCI boards, offering true alternatives even to small multi-processor systems.

# AMS Subject Classification (MSC 2000)

- 65Y10 Numerical analysis: Algorithms for specific classes of architectures

- 68U10 Computer science: Image processing

# ACM Computing Classification System (CSS 1998)

- G.4 Mathematical Software: Efficiency, Reliability and robustness, Parallel and vector implementations

- I.4.3 [Image Processing and Computer Vision]: Enhancement—Smoothing, Registration

- **I.4.6** [Image Processing and Computer Vision]: Segmentation—Region growing and partitioning

- **G.1.8** [Numerical Analysis]: Partial Differential Equations—Finite element methods, Finite difference methods, Parabolic equations, Hyperbolic equations, Multigrid and multilevel methods

- B.3.1 [Memory Structures] Semiconductor Memories—Dynamic memory (DRAM)

- I.3.1 [Computer Graphics]: Hardware Architecture—Graphics processors

- **B.7.1** [Integrated Circuits]: Types and Design Styles—Gate arrays

- C.1.3 [Processor Architectures]: Other Architecture Styles—Adaptable architectures

- C.4 Performance of Systems: Performance attributes

- J.3 Life and Medical Sciences: Health

General Terms: Algorithms, Languages, Performance, Theory

# Keywords

quantization, qualitative error control, quantized scale-space, memory gap, performance, datastream-based processing, graphics hardware, reconfigurable logic, reconfigurable computing

# **1** Introduction

### Contents

| 1.1 | Motiva  | ation                                     | 2  |

|-----|---------|-------------------------------------------|----|

|     | 1.1.1   | Operation Count and Performance           | 2  |

|     | 1.1.2   | Precision and Accuracy                    | 3  |

|     | 1.1.3   | Choice of Applications and Architectures  | 3  |

| 1.2 | Thesis  | Guide                                     | 5  |

|     | 1.2.1   | Thesis Structure                          | 5  |

|     | 1.2.2   | Index and Acronyms                        | 5  |

|     | 1.2.3   | Notation                                  | 6  |

|     | 1.2.4   | Binary Prefixes                           | 7  |

| 1.3 | Summ    | ary                                       | 8  |

|     | 1.3.1   | PDE Solvers in Quantized Image Processing | 8  |

|     | 1.3.2   | Data Processing                           | 10 |

|     | 1.3.3   | Hardware Efficient Implementations        | 10 |

| Ack | nowledg | gments                                    | 11 |

### **Tables**

| 1.1 | General notation.                          | 6 |

|-----|--------------------------------------------|---|

| 1.2 | International decimal and binary prefixes. | 7 |

The motivation section presents the broader picture of the thesis and outlines ideas which embrace the different chapters. In the Thesis Guide we present a quick overview of the thesis and cover presentational aspects. The chapter ends with a summary of the results and acknowledgments.

# **1.1 Motivation**

Numerical mathematics is concerned with the design of fast and accurate schemes for the approximate solution of mathematical problems. Computer systems are the target platforms for the implementation of theses schemes. So the trade-off between the competing factors of performance and accuracy applies both to the mathematical level where approximations of different accuracy order are chosen, and the implementational level where number formats and operations of different precision are used. Traditionally, the optimization processes are performed separately by mathematicians and computer scientists respectively. The common interface is the operation count of a scheme which is sought to be reduced. We argue that this measure is much too simple as it completely ignores the diverse performance characteristics of computer systems. Thus apparently efficient mathematical schemes perform surprisingly badly on actual systems. In the area of partial differential equation (PDE) based image processing the thesis demonstrates how an early consideration of performance relevant hardware aspects and a close coupling of the scheme design and its implementation fully exploit the available resources and so deliver fast and accurate solutions.

# **1.1.1 Operation Count and Performance**

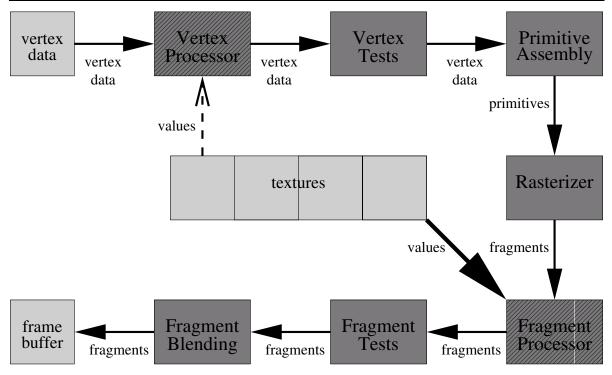

The merits of the exponential development in semiconductors have benefited memory and computing elements in different respects. Data transport and data processing have not developed at the same pace. The consequences are far-reaching but can be outlined by an example.

If we consider a simple addition of two vectors  $\overline{C} = \overline{A} + \overline{B}$  of size N, then the operation count is N. Modern micro-processors can process two operands made up of four 32-bit floats in one clock cycle. So if the processor runs at 3GHz it can perform 12G floating point OPS (FLOPS) and we should finish the addition in N/12 ns. Real performance values are at least an order of magnitude lower. The processor can really run almost 12G FLOPS if not disturbed by anything else, but the data cannot be transported that quickly. The parallel operations namely require 96GB/s of input data and 48GB/s for the output. But the current memory systems can provide a *bandwidth* of at most 6.4GB/s. This means that the computational unit spends 95% of time waiting for the data. So global data movement and not local computations are expensive and decisive for the overall performance.

The situation becomes even worse when the components of the vectors  $\overline{A}$ ,  $\overline{B}$  are not arranged one after another in memory, e.g. if they are part of larger structures or arranged in irregular lists. Then memory *latency*, the time needed to find the individual components in memory, becomes dominant and the performance can drop by as much as an order of magnitude again. Therefore, it is often advisable to enforce a linear arrangement of vector components, even if this means the inclusion of additional entries to fill up the gaps of the irregular arrangement. The operation count is increased, but the data can be processed in a seamless data stream, avoiding the latencies.

These two components data addressing and data transport dominate the execution times of

many algorithms. This fact has been acknowledged for some time already, and remedies have been developed, but the problem grows with each generation of new processors. Meanwhile hardware architectures subscribing to a data oriented computing paradigm have evolved. We evaluate three different representatives of this concept on image processing applications. The results show that the focus on regular data handling instead of minimal operation count delivers superior results.

# 1.1.2 Precision and Accuracy

In image processing applications performance is very critical. For this purpose one is often prepared to sacrifice strict accuracy requirements as long the quality of the results does not suffer significantly. The question arises how can we secure robust results with less precise computations.

A number format has only finitely many representations for the real numbers in a computer. So beside the error introduced by the discretization of the continuous PDE models, we also have an additional error associated with the quantized number representation and the approximate computations. Thus the quality of the final result depends both on the precision of the quantization and the properties of the schemes. It is very dangerous to trust in high precision alone. The simple computation  $1 - 1.0002 \cdot 0.9998$  in the single float format, for example, evaluates to zero, although the correct result  $4 \cdot 10^{-8}$  can be represented exactly. Even long double float formats do not save us from these problems (see Section 2.2.2.1 on page 27).

But for the sake of performance we want to operate on much smaller number formats, e.g. 8-16 bit. The mathematical challenge is to design schemes which can still deliver satisfactory results in this setting. For one iteration of a scheme strict error bounds can be derived. But these bounds avail to nothing if we iterate the scheme up to several hundred times. Since the number of iterations is sometimes even larger than the number of representable values in the number format (256 for 8 bit), all hope concerning accuracy seems to be lost. In fact, accuracy in the usual sense of error bounds which quantitatively relate the computed to the continuous solution cannot be obtained for such low precision. But the quality of the results depends not necessarily on this quantitative relation, but rather the qualitative behavior of the PDE model. So the guiding idea is to preserve invariants and characteristics of the evolution of the continuous models. These properties depend more on the appropriate design of the quantitative error we obtain accurate results in the sense of reproduced qualitative properties.

## **1.1.3 Choice of Applications and Architectures**

We have chosen the field of image processing, because it favors the use of parallel computations, which are widely used by our architectures, and allows the qualitative computational approach discussed in the previous section. We intentionally did not restrict ourselves to the study of discrete algorithms, but chose the PDE based models to demonstrate that the continuous properties can be preserved even with low precision computations. Having the continuous models in the background has also the advantage that from their analysis one knows a-priori which qualitative properties of the evolution are desirable and how they are influenced by the parameters. There is no dependence on the discrete nature of a computing model at the continuous stage, so that all such effects can be more easily identified in the implementation.

The choice of architectures has been motivated by the focus on processing in data streams as discussed in Section 1.1.1 on page 2. We evaluate three different architectures: graphics hardware, reconfigurable logic and reconfigurable computing devices. Their way to performance gains is similar: massive parallelism and efficient memory usage, but the programming models are quite different. To fortify the practicability of the presented approach to image processing, we have deliberately selected architectures which are available on affordable AGP or PCI accelerator boards and can be used with a standard Personal Computer (PC). The processing capabilities of graphics hardware even come for free, since every current PC already contains a powerful Graphics Processor Unit (GPU).

Throughout the thesis we argue strongly for the early consideration of hardware characteristics in the design of numerical solvers. However, this does not mean that we favor machineintimate, low level languages over standardized High Level Languages (HLLs). Although Hardware Description Languages (HDLs) offer more opportunities to utilize the full potential of the hardware, they have several disadvantages concerning the design effort, code reuse, compatibility and maintenance. We do not advocate the change from the currently predominant extreme of 'hardware blind' programming, to the other extreme of low level HDLs. The primary advantages of data oriented architectures can be exploited with high level considerations about the arrangement of data, memory access and the use of parallel processing elements (PEs). In most of our implementations we had to resort to low level languages only because standard HLLs are basically blind to hardware aspects and hardware efficient HLLs are yet in the development. We hope that these new HLLs will soon allow to solve problems of much higher complexity with full hardware support.

Despite the high parallelism of the architectures and good applicability to the image processing tasks we have restricted the implementations to 2D data sets. The PDE models and the quantized schemes can be extended to 3D easily. The implementations require reorganization to a different extent for 3D, but basically no new implementational ideas are involved. The reason why we do not present 3D examples, is our conviction that adaptive methods are indispensable for three dimensions. Even the massive parallelism of our architectures cannot compete with adaptive methods if data volume grows cubically. Naturally, adaptivity in 2D can also gain performance, but because of the trade-off between operation count and regular data access (Section 1.1.1 on page 2) the advantages are less striking. Initial work on hardware efficient adaptive 3D methods has already been performed and will be continued, but it is an extensive topic on its own facing many new challenges and therefore is not part of this thesis.

# 1.2 Thesis Guide

This is a quick guide dealing with issues which concern the thesis as a whole.

# 1.2.1 Thesis Structure

The chapters begin with a list of contents, figures and tables, and a sketch of the discussed topics. The last section in each chapter contains a detailed summary of the themes with accurate references to the previous sections. It may serve as a good overview for someone familiar with the subject. For a first orientation we give very concise information on the contents and prerequisites of the following chapters. For a summary of the results we refer to Section 1.3 on page 8 at the end of this chapter.

• 2. PDE Solvers in Quantized Image Processing

Here we introduce the PDE models for image processing and perform analysis of the properties of the discrete, quantized solvers. The chapter assumes a general understanding of PDEs and Finite Element (FE) methods. It is fairly independent of the other material. Mathematicians not interested in the reasoning about the implementation may want to proceed, after the quantized scheme analysis in each section, directly to the corresponding result sections in Chapter 4.

• 3. Data Processing

This chapter explains the reasons for the *memory gap* problem and how the different computing paradigms deal with it. It describes the suitability of various hardware architectures for image processing algorithms and thus motivates the selected devices used in Chapter 4. The chapter is basically self-contained and assumes only very basic knowledge about computer systems.

• 4. Hardware Efficient Implementations

Chapter 4 picks up the quantized schemes from Chapter 2 and discusses their efficient implementation under the considerations from Chapter 3. For readers interested mainly in the implementations it is probably best to get first an idea of the continuous model properties in Section 2.1 on page 15, and then continue with the corresponding implementation section in Chapter 4. The chapter does not assume familiarity with the non-standard architectures used, but for those new to this subject we recommend reading Chapter 3 for a broader picture and a better understanding.

# 1.2.2 Index and Acronyms

The index contains a list of key words. Referenced occurrences of these terms appear in *italic* in the text. *Bold italic* marks the main reference position for a term. At this position the meaning and context of the term can be found.

| Table 1.1 General notation.       |                                                                                                       |                               |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| Symbol                            | Example                                                                                               | Explanation                   |  |  |  |

| $u,\phi$                          | $u(x) = x^2$                                                                                          | continuous functions          |  |  |  |

| $U, \Phi$                         | $U(x) = \sum_{\alpha} \bar{U}_{\alpha} \Theta_{\alpha}(x),  (\Theta_{\alpha})_{\alpha} \text{ basis}$ | discrete functions            |  |  |  |

| $ar{U},ar{\Phi}$                  | $\bar{U}_{\alpha} = (\bar{U}_{(0,0)},, \bar{U}_{(N_x-1,0)},, \bar{U}_{(N_x-1,N_y-1)})^{\top}$         | nodal vectors                 |  |  |  |

| lpha,eta                          | $\alpha = (\alpha_x, \alpha_y) = (1, 2)$                                                              | 2D multi-indices              |  |  |  |

| $\mathcal{Q}$                     | $Q = \{\frac{n}{255}   n = 0, \dots, 255\}$                                                           | quantized number system       |  |  |  |

| $\oplus, \ominus, \odot, \oslash$ | $ar{V}\oplusar{W}$                                                                                    | quantized arithmetic          |  |  |  |

| $eval^{\mathcal{Q}}(term)$        | $\operatorname{eval}^{\mathcal{Q}}(\bar{V}-\bar{W})=\bar{V}\ominus\bar{W}$                            | quantized evaluation          |  |  |  |

| $=_{\mathcal{Q}}$                 | $\sqrt{\frac{1}{2}} = \mathcal{Q} \frac{180}{255}$                                                    | quantized evaluation          |  |  |  |

| g(.)                              | $g(x) = \exp(-c_g x)$                                                                                 | functions                     |  |  |  |

| f[.]                              | $f[u](x) = \int_0^x u(y) dy$                                                                          | operators                     |  |  |  |

| Symbol                            | Definition                                                                                            | Explanation                   |  |  |  |

| 1                                 | $\mathbb{1}(x) := x, \ (\mathbb{1}\bar{U})_{\alpha} := \bar{U}_{\alpha}$                              | continuous, discrete identity |  |  |  |

| $\bar{0}, \bar{1}$                | $\bar{0}:=(0,\ldots,0)^{\top},\ \bar{1}:=(1,\ldots,1)^{\top}$                                         | zero and one vector           |  |  |  |

| #                                 | $\#I:=\min_{f:I\to\mathbb{N} \text{ injective}} \max f(I)$                                            | number of elements in a set   |  |  |  |

| $\delta$                          | $\delta_{\alpha\beta} := \{1 \text{ if } \alpha = \beta; 0 \text{ else} \}$                           | Kronecker symbol              |  |  |  |

| diag                              | $\operatorname{diag}(L) := \left( \delta_{\alpha\beta} L_{\alpha\beta} \right)_{\alpha\beta}$         | diagonal of a matrix          |  |  |  |

| supp                              | $\mathrm{supp}\;(u){:=}\;\{x\in\Omega u(x)\neq 0\}, u:\Omega\to\mathbb{R}$                            | support of a function         |  |  |  |

Table 1.1 General notation.

Acronyms are written out in the long form at least once, when they appear first in the text. Their meaning is also explained in an alphabetical listing on page 201 just before the index.

# 1.2.3 Notation

Table 1.1 summerizes the general notation. Hereby, most continuous quantities involved in the PDE models are typed in small letters, e.g. u. The corresponding discrete functions are set in capital letters (U). The nodal vectors defining the discrete functions are marked by a bar  $(\overline{U})$  and addressed  $(\overline{U}_{\alpha})$  by two dimensional multi-indices, e.g.  $\alpha = (\alpha_x, \alpha_y) \in \mathbb{N} \times \mathbb{N}$ . For further details we refer to Section 2.2.1.2 on page 26.

The nodal vectors are generally assumed to be already quantized elements of some quantization Q. Quantized arithmetic operations are denoted by  $\odot \in \{\oplus, \ominus, \odot, \odot\}$  (Section 2.2.3.1 on page 36). Quantized evaluations of terms are written as  $eval^{Q}(term)$  or  $=_{Q}$  (Section 2.2.3.2 on page 38).

|   |           |         | • 1     |          |        |        |  |

|---|-----------|---------|---------|----------|--------|--------|--|

| Ι | Decimal   | Decimal | Decimal | Binary   | Binary | Binary |  |

|   | factor    | name    | symbol  | factor   | name   | symbol |  |

|   | $10^{3}$  | kilo    | k       | $2^{10}$ | kibi   | Ki     |  |

|   | $10^{6}$  | mega    | М       | $2^{20}$ | mebi   | Mi     |  |

|   | $10^{9}$  | giga    | G       | $2^{30}$ | gibi   | Gi     |  |

|   | $10^{12}$ | tera    | Т       | $2^{40}$ | tebi   | Ti     |  |

|   | $10^{15}$ | peta    | Р       | $2^{50}$ | pebi   | Pi     |  |

|   | $10^{18}$ | exa     | Е       | $2^{60}$ | exbi   | Ei     |  |

|   |           | •       |         | •        | •      |        |  |

Table 1.2 International decimal and binary prefixes.

We distinguish between functions g(u(x)) and operators f[u](x) with different brackets. The first case is actually a composition of functions  $(g \circ u)(x)$  and represents the value of the function g at the position u(x). In the second case f is an operator which takes the function u as an argument and returns a new function f[u] as a result. This new function is then evaluated at x.

For clarity, we keep up this distinction in the discrete case, e.g.  $G(\overline{V}), L[\overline{V}]$ , although a discrete operator could also be seen as a high dimensional function of the finitely many vector components.

# 1.2.4 Binary Prefixes

There is a confusion about the use of the Système International d'Unités (SI)-prefixes in computer science, where typically the binary system is used and byte (B) or bit (b) quantities are multiples of 2. When the referred numbers were small the capitalization of 1kB = 1000Bto 1KB = 1024B provided an appropriate distinction, but this does not apply to the larger prefixes, e.g. 1MB has been used for both 1,000,000B and  $1024^2B = 1,048,576B$  depending on the context.

Since 1999 there exists an international standard on the naming of  $2^{10n}$  factors [IEC, 2000]. Table 1.2 presents the decimal and binary symbols and names. Initially the standard has been generally ignored, but the approval of the symbols by the Linux developers in 2001 and the trial-use announcements by the Institute of Electrical and Electronics Engineers (IEEE) and American National Standards Institute (ANSI) in 2002 have helped to widen its popularity. We make use of the handy distinction throughout the work and also translate quantities from other sources into this terminology. Where the sources are not totally clear which prefixes were meant we have made a choice to the best of our knowledge.

Due to the organization of memory (see Section 3.1.1 on page 71), sizes of memory chips, caches and sizes of data objects stored therein use almost exclusively the binary factors, while

*bandwidth* and *throughput* are expressed with the decimal factors, because they are based on frequencies given in MHz or GHz. For mass storage devices the situation is inconsistent with the capacity of hard discs, DVDs and most other disk or tape devices being given in the decimal system, while the dimensions of CDs and flash memory based devices (USB sticks, CompactFlash cards, etc.), and the file sizes in operating systems are calculated in the binary system, but displayed misleadingly with the decimal factors. The confusion is complete for floppy disks where '1.44MB' means neither 1.44MB nor 1.44MiB but 1,440KiB, which is twice the capacity of old 720KiB disks and derived as  $512B(\text{sector size}) \cdot 9(\text{sectors/track}) \cdot 80(\text{tracks}) \cdot 2(\text{sides}) = 720\text{KiB}$ . Although current disk and tape devices use also binary sector sizes like 1KiB or 4KiB for the smallest storable data block, similar to the floppy disk their arrangement does not depend on powers of two, so that the more marketing friendly decimal factors are used.

# 1.3 Summary

The main contribution of the thesis is the close coupling of the numerical scheme design with the implementation. Careful treatment of roundoff behavior in the discrete PDE solvers secures qualitatively accurate results despite strong quantization, and thorough consideration of the performance characteristics of the hardware architectures delivers high performance. The numerical and hardware aspects, which are usually dealt with separately by mathematicians and computer scientists, receive here an integral treatment to the benefit of both performance and accuracy.

The following sections summarize the individual chapters. For a very concise overview and prerequisites of the chapters see Section 1.2.1 on page 5.

# 1.3.1 PDE Solvers in Quantized Image Processing

We deal with three important application areas of image processing: denoising, segmentation and registration (Section 2.1 on page 15). The solution to these problems is often needed in real-time, such that the requirements on performance are very high. Each task is modeled by a PDE and an approximate, numerical solution can be obtained after time and space discretization (Section 2.2 on page 24). Bounds on the difference between the continuous and discrete solution exist, but these bounds assume error-free computations. In real computer systems quantization as a third source of error comes into play.

It is very important to realize that even high precision floating point formats such as long double (s63e15) can easily lead to completely wrong results for simple computations (Section 2.2.2.1 on page 27). In PDE solvers many iterative computations must be performed, so that one cannot trust in high precision number formats alone. Deterministic, probabilistic and empirical methods can be used to derive bounds for the quantization errors of algorithms. But because of the very high performance requirements, image processing algorithms tend to use

low precision fixed point number systems (Section 2.2.2.2 on page 30). For these systems it is impossible to guarantee numerical stability of iterative schemes in neither deterministic nor probabilistic sense (Section 2.2.2.3 on page 33). In practice, empirical evidence from error simulators and test suits is used on a case by case basis to estimate the effects of quantization for a given algorithm. But this is a time consuming and intransparent procedure. Moreover, the empirical evidence cannot guarantee the desired behavior for all possible input data.

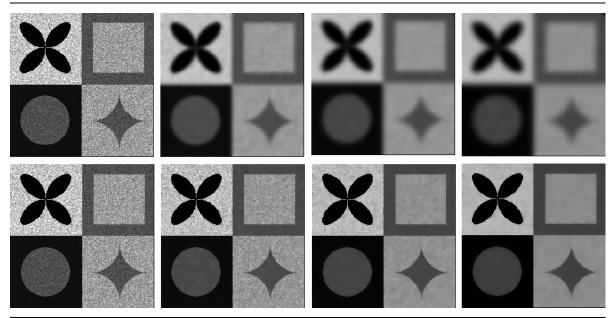

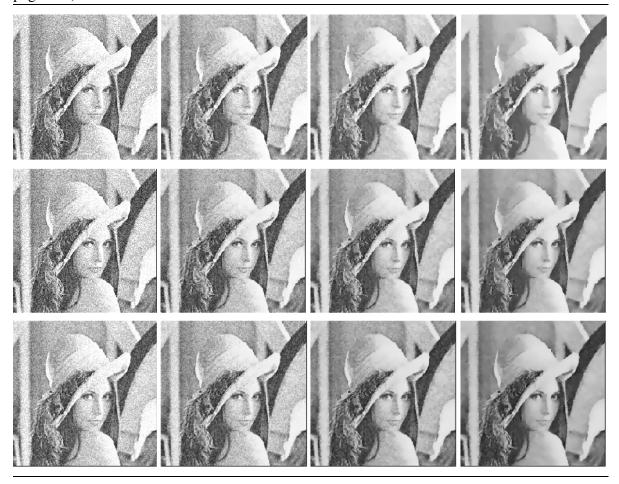

The main result of Chapter 2 is the design of discrete schemes which can guarantee a certain behavior of the quantized PDE solvers despite strong quantization. The key idea is to preserve the desired global properties of the continuous model rather than try to control the accuracy of individual computations. Hereby, the factorization and aggregation of numbers on different scales and the interactions between different node values deserve special attention (Sections 2.3.1 on page 43, 2.4.1 on page 55, 2.5.1 on page 59). In particular, a careful implementation of the matrix vector product as a main ingredient of the discrete schemes is decisive. Involved symmetric matrices have often unit column sums ( $\forall j : \sum_i A_{ij} = 1$ ) preserving the overall mass (sum of the vector components) in a matrix vector product (Eq. 2.26 on page 39). In low precision arithmetic underflows can easily violate the mass preservation and other global properties, and the iterative nature of the algorithm quickly accumulates these errors to produce visual artefacts (Figure 4.8 on page 140). The *mass-exact matrix vector product* (Section 2.2.3.3 on page 39) guarantees the mass preservation irrespective of the used quantization. Moreover, it is well suited for the field of image processing as it operates with highest accuracy around edges (Section 2.2.3.5 on page 42).

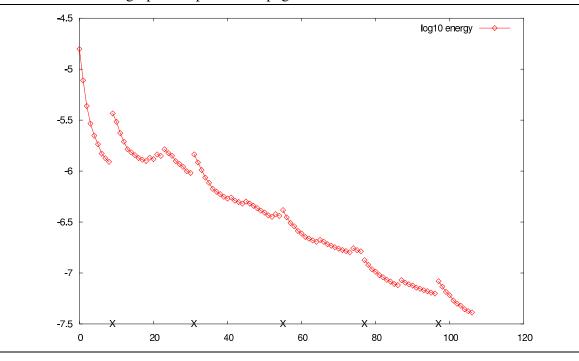

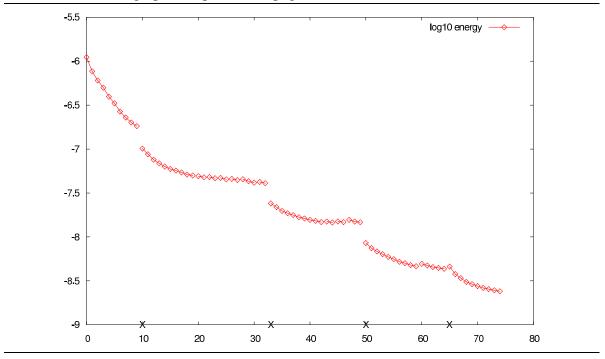

When used in the *anisotropic diffusion* scheme the mass-exact matrix vector product also secures other important properties of the quantized scale-space (Section 2.3.3 on page 49), most notably the extremum principle (Eq. 2.53 on page 51) and Lyapunov functionals (Eq. 2.57 on page 52). The derivation of the quantized scale-space is a very satisfactory result, as it inherits almost all of the properties of the continuous scale-space of the anisotropic diffusion operator (Section 2.1.1.2 on page 17). In particular, the decrease of energy, central moments and the increase of entropy follow for arbitrary quantizations.

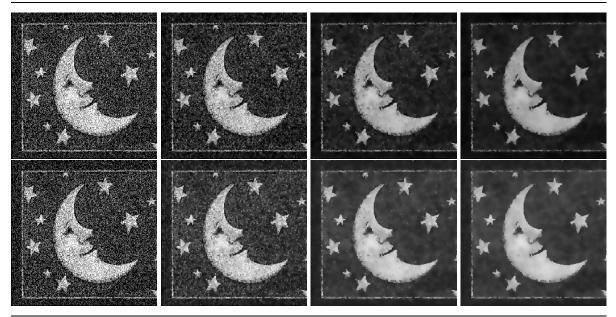

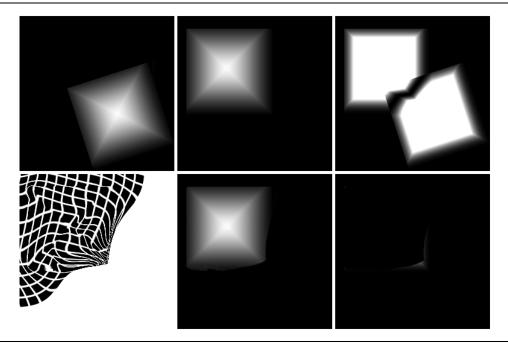

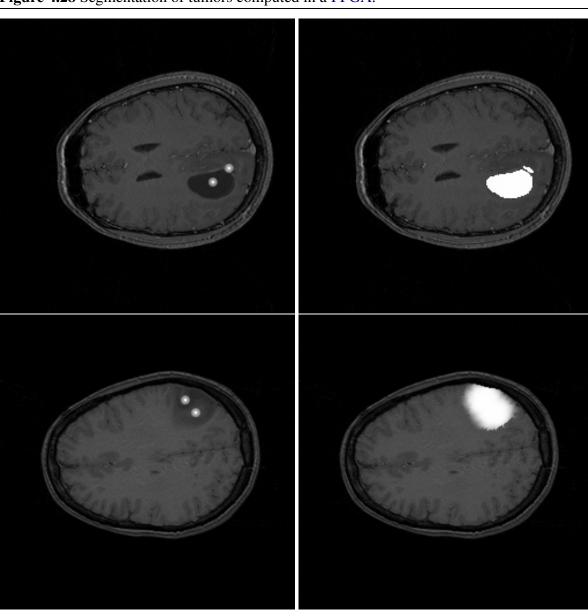

In case of the *level-set equation* used for segmentation we have put the focus on the best possible resolution of different velocities during the evolution of the interface. Clearly the quantization restricts the number of distinct velocities, but scaling schemes can secure that the faster moving parts evolve with the highest available precision. Moreover, the stationary asymptotic behavior equals the continuous model (Section 2.4.3 on page 58).

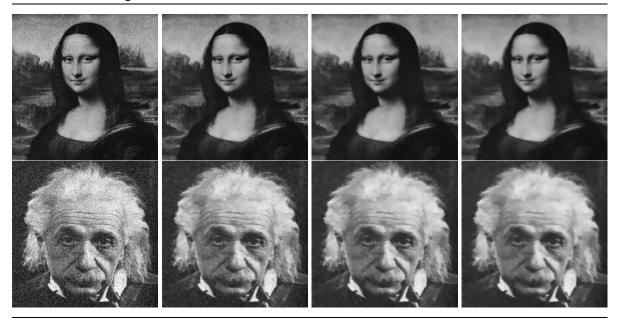

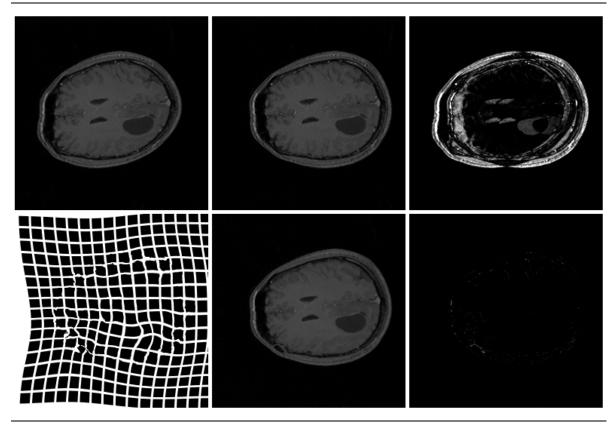

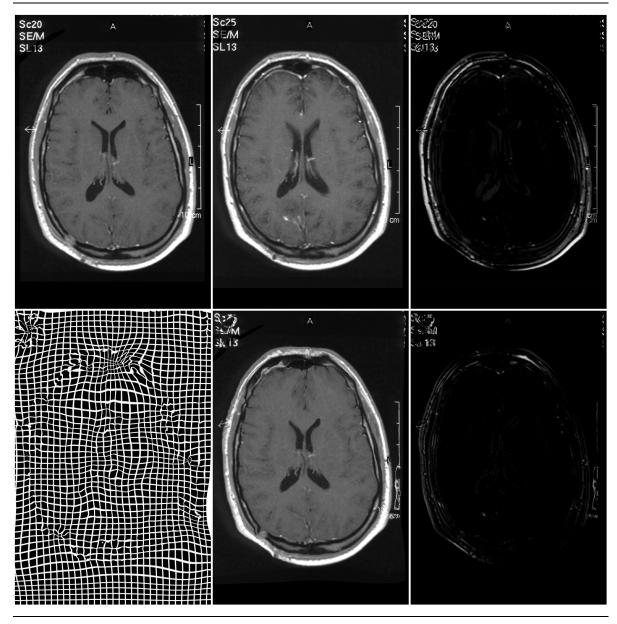

The multi-scale regularization of the registration problem makes the quantized scheme very robust against quantization errors. Cutting the precision of the used number format in half hardly changes the results (Section 4.1.5.2 on page 147). This is also achieved by the robust diffusion schemes used in the regularization at various stages. So despite the high complexity of the algorithm and numerous intermediate result stages, the quality of the low precision results is not corrupted by roundoff errors.

The design of the robust schemes partly depends on a space discretization with an equidistant grid (Section 2.2.1.2 on page 26). This impedes dynamic adaptivity, but trading operation

count for a regular memory access pattern (Section 1.1.1 on page 2) is often advantageous, because the regular data-flow of the image processing applications (Section 2.6 on page 63) makes them suitable for highly parallel architectures.

# 1.3.2 Data Processing

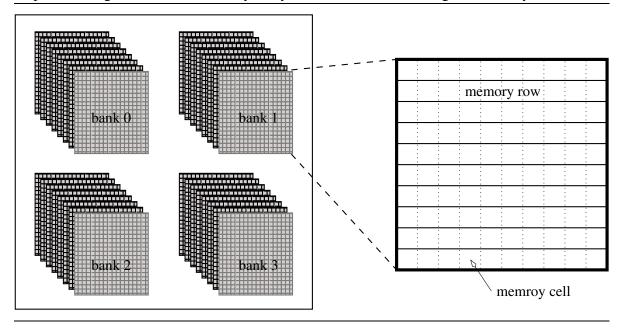

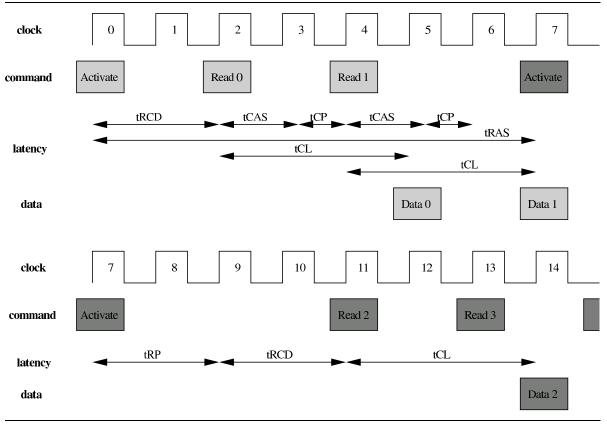

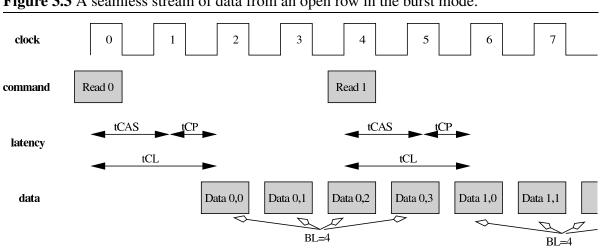

The exponential growth of transistors on the same area of silicon has influenced the characteristics of memory and computing logic differently (Section 3.1 on page 71). This is not a necessity but economical forces steer the development to a great extent. With smaller feature sizes the timings of PEs and the size of Dynamic RAM (DRAM) chips have risen exponentially, but the timings of the memory core which stores the 0s and 1s have improved in comparison very little (Section 3.1.1.1 on page 72). An order of magnitude lies between each of the times needed for the addition of two numbers, their transport to the processor and their localization in the memory in case of a random memory access.

The problem of diverging memory and logic performance, labeled *memory gap*, grows each year, and from an economic point of view there is no remedy in sight. Current improvements benefit mainly *bandwidth*, while in comparison *latency* even worsens (Section 3.1.1.2 on page 76). For optimal performance almost all latencies can be hidden, but this requires a predictable data-flow of the algorithm. Processing of data in streams and maximal data reuse in memory hierarchies (Section 3.1.3 on page 81) have become very beneficial for performance.

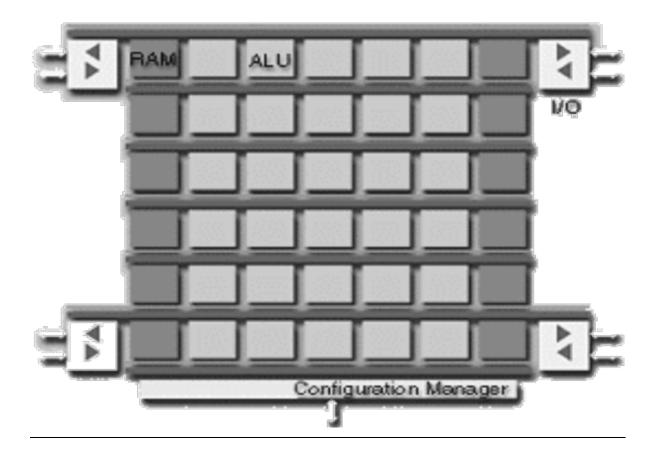

In view of the memory gap, Chapter 3 irradiates different computing paradigms (Section 3.2 on page 84), parallelization options (Section 3.2.2 on page 87), the status quo of current hard-ware architectures (Section 3.3.1 on page 97) and the future evolution of computing machines (Section 3.3.2 on page 103). The resource utilization of multiple PEs with different types of *parallelism* and the minimization of bandwidth and latency requirements play a decisive role in these sections. But in many cases the availability of high level programming tools rather than the characteristics of the hardware matter for the economic success of an architecture. The easy serial programming model has mainly prevailed over performance considerations so far, but the sheer number of new architectures (Sections 3.2.4 on page 93, 3.2.5 on page 96), many of which are available as commercial products, indicates that the performance gains are too large to be still ignored. The quantized schemes for the image processing tasks from Chapter 2 are particularly suitable for the acceleration on these new devices.

## **1.3.3 Hardware Efficient Implementations**

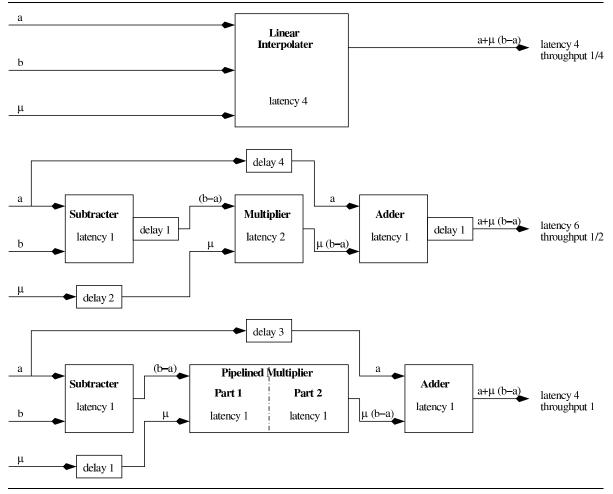

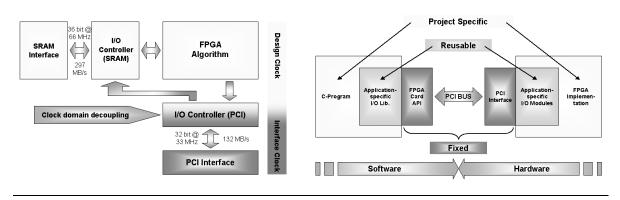

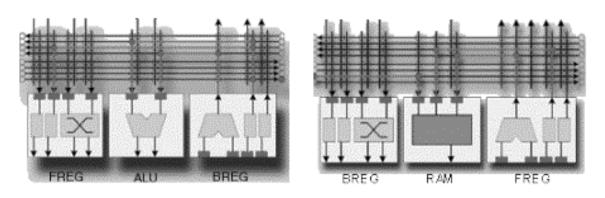

Three data-stream-based (DSB) architectures have been used for the implementation of the image processing applications: GPUs, a Field Programmable Gate Array (FPGA) and the eX-treme Processing Platform (XPP). The distribution of the solvers on the architectures reflects their availability and ease of operation. GPUs are the most common and inexpensive, and have been used for several implementations. Availability of FPGAs is high, but not so much the costs of the hardware but those of the development tools pose higher barriers to common

usage. Finally, the coarse-grain XPP array has only been available for a limited period of time as a clock cycle exact simulator. But now a PCI card with that device can be purchased.

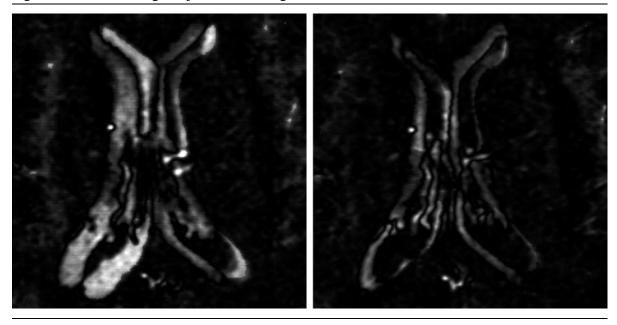

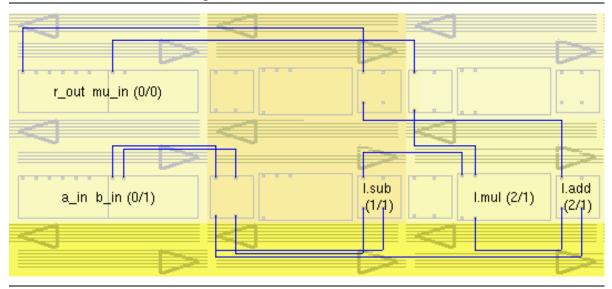

The early implementations of the diffusion models and the level-set equation in graphics hardware (Sections 4.1.3 on page 127 and 4.1.4 on page 132) demonstrated the applicability of GPUs as scientific coprocessors and inspired other work in that area. The *virtual signed 16 bit format* (Figure 4.10 on page 141) was the first to overcome the 8 bit limitation of GPUs in general, providing more suitability for scientific computations (Figure 4.11 on page 142). On newer hardware more advanced numerical concepts such as multi-scale representation, multi-grid solvers and adaptive time-step control have been realized for the registration problem (Section 4.1.5 on page 143). Although the other architectures offer even higher resource utilization, the GPU has now the advantage of a high level access to its functionality which greatly facilitates the programming. The complex algorithm for the registration would be very difficult to code on a FPGA or the XPP.

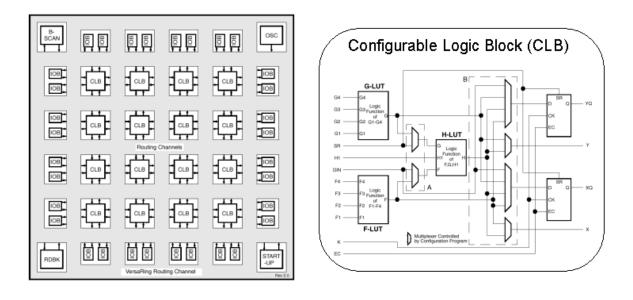

The FPGA implementation of the level-set equation exploits the full flexibility of the low level reconfigurability (Section 4.2.3 on page 161). Application specific data paths and operations, and *variable precision arithmetic* bring the small device (approx. one third of a DX8 GPU) in lead of much larger and higher clocked processors. More recent FPGAs can further increase performance of such algorithms by utilizing embedded hardwired multipliers, which otherwise consume a lot of configurable resources.

The size of the XPP64-A1 architecture is comparable to a DX8 GPU (approx. 50M transistors), but its flexible access to massive parallelism beats the competitors (Section 4.3.3 on page 175). Similar to the FPGA the whole scheme is merged into a fully pipelined super computation unit which delivers a result pixel in each clock cycle.

Despite the low precision number formats available on the devices, the special quantized schemes from Chapter 2 allow to retain the main properties of the continuous models. At the same time the implementations can outperform a comparable micro-processor by factors of 5 to 20. Thus the goal of fast low precision computations with preserved global properties has been reached. The current hardware development and the better scalability of the architectures suggest that these factors will grow further in future. Concurrently, the complexity of the problems will increase and the availability of hardware efficient High Level Language will gain even more relevance for the broad success of these architectures.

# Acknowledgments

First of all my thanks goes to my advisor Martin Rumpf who encouraged me to work on this interdisciplinary topic and supported me in the sometimes difficult advancement of the research. I am particularly grateful for his initiative towards the use of different hardware architectures, which lead to a broader and more abstract perspective on the topic.

During the work I have received plenty of help from my colleagues and the administration of

the Institute of Applied Mathematics at the University of Bonn and the Numerical Analysis and Scientific Computing group at the University of Duisburg-Essen. In Bonn, Ralf Neubauer and Michael Spielberg were very helpful in designing the first implementations, Thomas Gerstner worked with me on volume rendering and Jochen Garcke often helped with computer problems. In the difficult beginning the former PhD students Martin Metscher and Olga Wilderotter offered advice. Both in Bonn and Duisburg the development of the applications was expertly supported by Tobias Preusser, Marc Droske and Ulrich Clarenz. Udo Diewald was an unebbing source of helpful tips and information, and Ulrich Weikard, my room mate in Duisburg, was always ready for an inspiring discussion. He and Martin Lenz proof-read and discussed the thesis with me. Martin's scientific vicinity to parts of the thesis also helped me with some complex improvements of it. Special mention deserves Birgit Dunkel, our ever helpful secretary in Duisburg. Many thanks to all my colleagues for their different contributions to the success of this work.

I am also grateful to many persons of other facilities who have helped me in various ways. The successful research with Oliver Junge and Michael Dellnitz from the University of Paderborn brought about my first scientific publication and fortified my decision towards this thesis. The German National Academic Foundation supported me during my PhD allowing me to participate in many stimulating discussions. Heinz-Josef Fabry from the Faculty of Catholic Theology at the University of Bonn was my consultant and gave me much insight outside of the mathematical universe. The work of Matthias Hopf and Thomas Ertl from the University of Stuttgart made me aware of the looming computing potential in graphics hardware. The fruitful discussions with Matthias also helped me with the peculiarities of early graphics hardware. Markus Ernst, Steffen Klupsch and Sorin Huss from the Technical University of Darmstadt introduced me to the world of Reconfigurable Logic. Markus and Steffen directly contributed to the thesis by coding the hardware configuration for the level-set equation on a FPGA. The company PACT XPP Technologies from Munich granted me a temporary free research license to work with their XPP architecture and Prashant Rao readily answered my questions concerning its programming. In late 2002 I joined the caesar research center in Bonn directed by Karl-Heinz Hoffmann, who has generously supported my further research. Although the recent results are not directly included in this thesis my coworkers have positively influenced its contents. I am indebted to Marcus Magnor and Ivo Ihrke from the Max Planck Institute for Computer Science in Saarbrücken, Alexandru Telea from the Technical University of Eindhoven, Aaron Lefohn and John Owens from the University of California, Davis, Ross Whitaker from the University of Utah, Salt Lake City, and Christoph Garbe from the University of Heidelberg for inspiring discussions.

In such long lasting work not only the scientific but also the social support is of great importance. Special thanks to my friends and above all my parents and brothers and sisters who accompanied me through the highs and lows. Their constant encouragement made this work possible.

# 2 PDE Solvers in Quantized Image Processing

# Contents

| 2.1 | Contin | inuous PDE Based Image Processing |                              |    |  |  |  |

|-----|--------|-----------------------------------|------------------------------|----|--|--|--|

|     | 2.1.1  | Denoising - Diffusion Processes   |                              |    |  |  |  |

|     |        | 2.1.1.1 Generic Diffusion Model   |                              |    |  |  |  |

|     |        | 2.1.1.2                           | Scale-Space                  | 17 |  |  |  |

|     |        | 2.1.1.3                           | Related Work                 | 19 |  |  |  |

|     | 2.1.2  | Segment                           | ation - Level-Set Methods    | 19 |  |  |  |

|     |        | 2.1.2.1                           | Curve Evolution              | 19 |  |  |  |

|     |        | 2.1.2.2                           | Hamilton-Jacobi Equation     | 21 |  |  |  |

|     |        | 2.1.2.3                           | Related Work                 | 21 |  |  |  |

|     | 2.1.3  | Registrat                         | tion - Energy Gradient Flows | 22 |  |  |  |

|     |        | 2.1.3.1                           | Energy Model                 | 22 |  |  |  |

|     |        | 2.1.3.2                           | Multi-Scale Hierarchy        | 23 |  |  |  |

|     |        | 2.1.3.3                           | Related Work                 | 24 |  |  |  |

| 2.2 | Discre | retization - Quantization         |                              |    |  |  |  |

|     | 2.2.1  | Discrete                          | Operators                    | 24 |  |  |  |

|     |        | 2.2.1.1                           | Time Discretization          | 25 |  |  |  |

|     |        | 2.2.1.2                           | Space Discretization         | 26 |  |  |  |

|     | 2.2.2  | Quantiza                          | tion                         | 26 |  |  |  |

|     |        | 2.2.2.1                           | Floating Point Numbers       | 27 |  |  |  |

|     |        | 2.2.2.2                           | Fixed Point Numbers          | 30 |  |  |  |

|     |        | 2.2.2.3                           | Numerical Stability          | 33 |  |  |  |

|     | 2.2.3  | Quantize                          | ed Operators                 | 36 |  |  |  |

|     |        | 2.2.3.1                           | Arithmetic Operations        | 36 |  |  |  |

|     |        | 2.2.3.2                           | Composed Operations          | 38 |  |  |  |

|     |        | 2.2.3.3                           | Matrix Vector Product        | 39 |  |  |  |

|     |        | 2.2.3.4                           | Scaling                      | 41 |  |  |  |

|     |        | 2.2.3.5                           | Backward Error               | 42 |  |  |  |

| 2.3 | Anisotropic Diffusion |                                   |    |  |  |  |

|-----|-----------------------|-----------------------------------|----|--|--|--|

|     | 2.3.1                 | FE Scheme                         |    |  |  |  |

|     |                       | 2.3.1.1 Discrete Schemes          | 44 |  |  |  |

|     |                       | 2.3.1.2 Weighted Stiffness Matrix | 45 |  |  |  |

|     | 2.3.2                 | Quantized Diffusion               | 48 |  |  |  |

|     | 2.3.3                 | Quantized Scale-Space             | 49 |  |  |  |

| 2.4 | Level-                | Set Segmentation                  | 55 |  |  |  |

|     | 2.4.1                 | Upwind Scheme                     | 55 |  |  |  |

|     | 2.4.2                 | Quantized Propagation             | 56 |  |  |  |

|     | 2.4.3                 | Asymptotic Behavior               | 58 |  |  |  |

| 2.5 | Gradi                 | ent Flow Registration             | 59 |  |  |  |

|     | 2.5.1                 | Multi-Grid Discretization         | 59 |  |  |  |

|     | 2.5.2                 | Quantized Registration            | 61 |  |  |  |

|     | 2.5.3                 | Quantized Descent                 | 62 |  |  |  |

| 2.6 | Data-l                | Flow                              | 63 |  |  |  |

|     | 2.6.1                 | Explicit and Implicit Schemes     | 63 |  |  |  |

|     | 2.6.2                 | Data Locality                     | 65 |  |  |  |

|     | 2.6.3                 | Local Computations                | 65 |  |  |  |

| 2.7 | Concl                 | usions                            | 67 |  |  |  |

|     |                       |                                   |    |  |  |  |

#### Figures

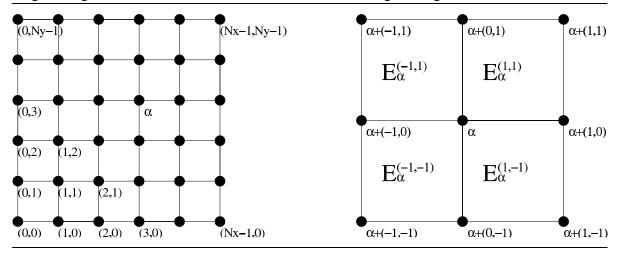

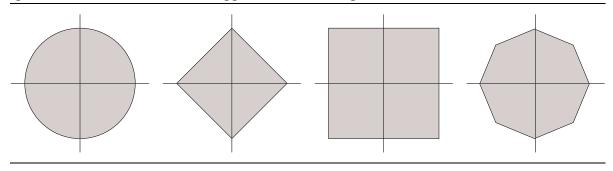

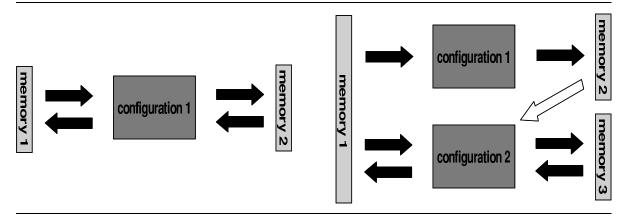

| <ul> <li>2.2 The unit spheres of different vector norms in 2D</li></ul> | 2.1 | An equidistant grid with enumerated nodes and elements | 27 |

|-------------------------------------------------------------------------|-----|--------------------------------------------------------|----|

| 2.3 High level data-flow of the PDE solvers                             | 2.2 | The unit spheres of different vector norms in 2D       | 57 |

|                                                                         | 2.3 | High level data-flow of the PDE solvers                | 64 |

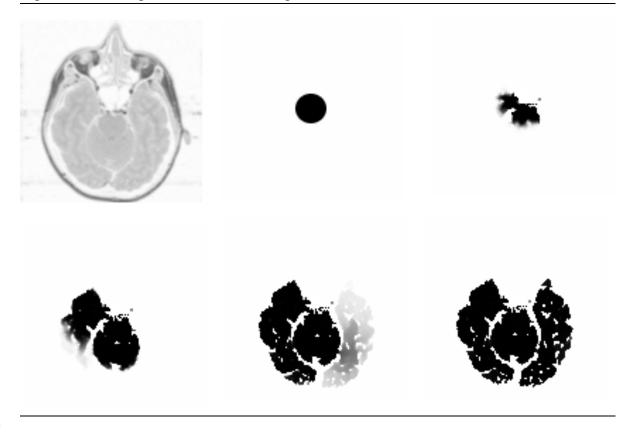

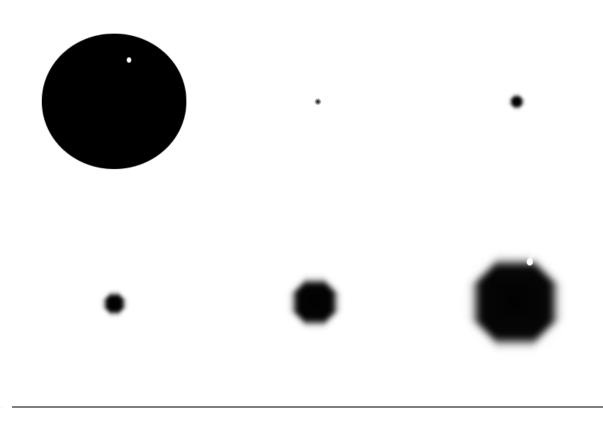

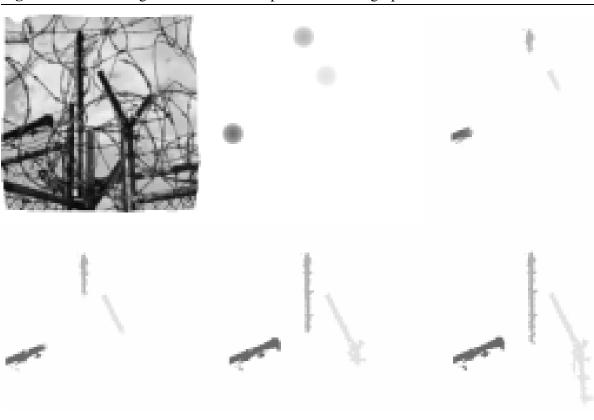

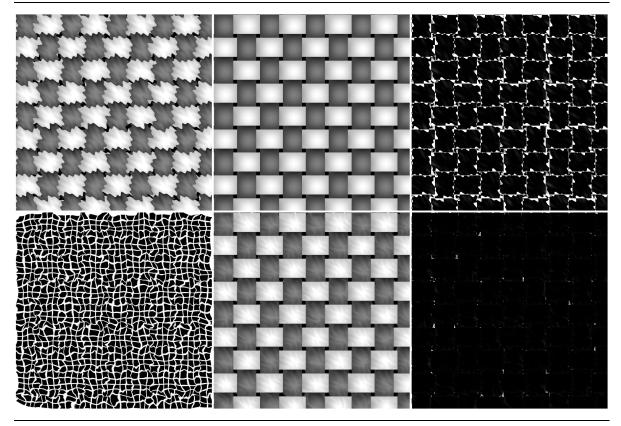

This chapter contains the theoretical analysis of different PDE based image processing algorithms with respect to quantization. For a given quantization every operation can be performed up to a certain precision. The aggregation of this effect is similar to the effects of time and space discretization of the continuous models and accordingly we are interested in convergence and approximation behavior. In particular for fixed point numbers, which exhibit large relative error in many computations, we find equivalent reformulations of the discrete solvers which reproduce their qualitative behavior even under strong quantization.

The problems of denoising, segmentation and registration are modeled by different differential equations, but their discretizations focus on the creation of a common regular data-flow. The choice of discretization is also influenced by the quantization since appropriate re-ordering of operations in the schemes allows to retain a higher accuracy. By paying attention to such issues the developed solvers unveil their sensitivity to hardware architectures and the performance benefits are discussed in Chapter 4 on page 107.

# 2.1 Continuous PDE Based Image Processing

Images undergo many modifications on the way from the acquisition to the output device. A typical series of processing stages includes:

- Reconstruction of the image data from the raw data of the acquisition device.

- Removal of unavoidable noise in the image due to the acquisition process.

- Identification of segments in the image which are of special interest to the application.

- Correlation of the image information with other images of similar content.

- Visualization of the image with regard to the characteristics of the human visual system.

Each of these tasks has drawn a lot of research attention. The first is a little less accessible, since the manufacturers of image acquisition devices usually know the peculiarities of their hardware best and already include the reconstruction into the device. The last task on the other hand is a very extensive field of its own, since the required form of data presentation varies widely from application to application.

Therefore, we restrict ourselves to the three central tasks of image denoising, segmentation and registration. Still there have been numerous ways of approaching these problems. We concentrate on continuous PDE models which encode the nature of the problem implicitly in functional equalities. This general choice of methods is motivated in Section 1.1.3 on page 3 in the introduction. The following sections review the PDE models associated with the three afore mentioned image processing tasks.

## 2.1.1 Denoising - Diffusion Processes

Image data often contains noise stemming from the acquisition or transmission process. If certain characteristics of the noise distribution are known, one usually incorporates appropriate filters into the acquisition or transmission process itself. In the absence of other a-priori knowledge, noise is often assumed to be normally distributed. A very simple but effective method for reducing such noise is the application of a Gaussian filter, which is related to a linear diffusion process. Unfortunately this technique also reduces highly relevant edge information in the image. Non-linear methods which aim at distinguishing between relevant image information which should be protected and noise fluctuations which should be removed are necessary for a feature sensitive denoising. The anisotropic diffusion model represents a class of these non-linear methods.

#### 2.1.1.1 Generic Diffusion Model

We consider the function  $u : \mathbb{R}^+ \times \Omega \to \mathbb{R}$  in the domain  $\Omega := [0, 1]^2$  and an initial noisy image given as a function  $u_0 : \Omega \to \mathbb{R}$ . The idea is to evolve the initial image through a partial

differential equation such that in the sequence of the resulting images u(t,.), t > 0 the noise dissolves while edges are preserved. The *generic diffusion* model reads:

(2.1)

$$\partial_t u - \operatorname{div} \left( G(\nabla u_\sigma) \nabla u \right) = 0 , \quad \text{in } \mathbb{R}^+ \times \Omega ,$$

$$u(0) = u_0 , \quad \text{on } \Omega ,$$

$$G(\nabla u_\sigma) \nabla u \cdot \nu = 0 , \quad \text{on } \mathbb{R}^+ \times \partial \Omega$$

where  $G : \mathbb{R} \to \mathbb{R}^{2 \times 2}$  is the *diffusion tensor* depending on a mollification  $u_{\sigma}$  of u. We may distinguish three major choices for G:

• *Linear diffusion* model  $G(\nabla u_{\sigma}) := \mathbb{1}$

In this case we have the linear heat equation:

$$\partial_t u - \Delta u = 0.$$

The solution can be obtained by convolution (denoted by '\*')

$$u(t) = \mathcal{G}_{0,\sqrt{2t}} * u_0,$$

with a Gaussian function

(2.2)

$$\mathcal{G}_{\mu,\sigma}(y) := (2\pi\sigma^2)^{-\frac{1}{2}} \exp\left(-\frac{1}{2}\frac{(y-\mu)^2}{\sigma^2}\right).$$

The parameter  $\mu$  is not required here, but will be needed later in a different context (Eq. 2.6 on page 20). According to this model the intensities in the image will dissolve homogenously in every direction and with equal rate at every position. This model is used for fast and simple smoothing and regularization, e.g. the mollification  $u_{\sigma}$  may be performed with the linear model:

$$u_{\sigma} := u(\sigma^2/2) = \mathcal{G}_{0,\sigma} * u_0$$

.

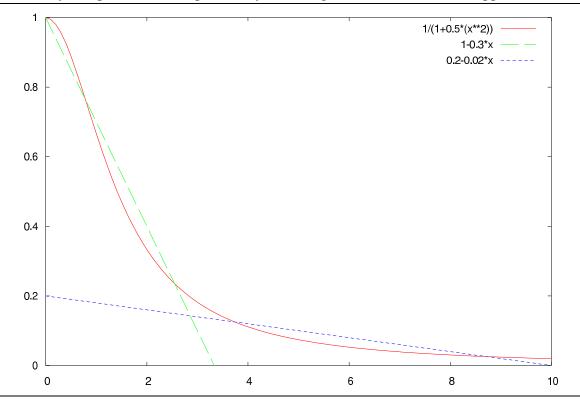

• Non-linear diffusion model  $G(\nabla u_{\sigma}) := \tilde{g}(\|\nabla u_{\sigma}\|) \mathbb{1}$

Here the diffusion tensor depends on a non-negative, monotone decreasing scalar function  $\tilde{g} : \mathbb{R} \to \mathbb{R}_0^+$ . A typical choice for  $\tilde{g}$  is the *Perona-Malik function*

(2.3)

$$\mathcal{P}_{c_{\tilde{g}}}(x) := \frac{1}{1 + c_{\tilde{g}}x^2}$$

or an exponential equivalent like  $\exp(-c_{\tilde{g}}x)$ , such that for large gradient modulus  $\|\nabla u_{\sigma}\|$  the function  $\tilde{g}$  has small values meaning small diffusion rate, and for small gradient modulus large values meaning high diffusion rate. The mollification  $u_{\sigma}$  helps to distinguish edges from singular high gradients due to noise. Consequently the diffusion rate in this model depends non-linearly on the modulus of the gradient of intensities at each position, but the diffusion direction is homogenous.

- Anisotropic diffusion model  $G(\nabla u_{\sigma}) := B(\nabla u_{\sigma})^{\top} g(\|\nabla u_{\sigma}\|) B(\nabla u_{\sigma})$

- This extends the previous model to a direction dependent diffusion rate. Now g is a diagonal matrix with independent diffusion coefficients for the direction along the smoothed gradient and orthogonal to it, while B is the transformation from the vectors in the canonical basis to the vectors in the gradient-normal basis:

(2.4)

$$B(\nabla u_{\sigma}) := \frac{1}{\|\nabla u_{\sigma}\|} \begin{pmatrix} \partial_{x} u_{\sigma} & \partial_{y} u_{\sigma} \\ -\partial_{y} u_{\sigma} & \partial_{x} u_{\sigma} \end{pmatrix},$$

$$g(\|\nabla u_{\sigma}\|) := \begin{pmatrix} g_{1}(\|\nabla u_{\sigma}\|) & 0 \\ 0 & g_{2}(\|\nabla u_{\sigma}\|) \end{pmatrix}$$

Typically  $g_1$  is chosen as the Perona-Malik function  $\mathcal{P}$  like in the previous case and  $g_2(x) = c_{g_2}$  is some positive constant. In contrast to the previous, this model can smooth distorted edges because diffusion will only be inhibited in the direction orthogonal to the edge, while the smoothing along the edge will still take place in the non-linear fashion.

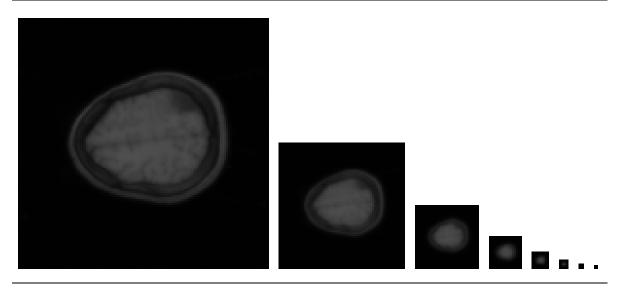

#### 2.1.1.2 Scale-Space

The solution  $u : \mathbb{R}^+ \times \Omega \to \mathbb{R}$  can be regarded as a multi-scale of successively diffused images  $u(t), t \ge 0$ , which is called the *scale-space* of  $u_0$ . We want to study the properties of this scale-space in the form of the corresponding scale-space operator  $S_t$ , which is defined as

$$S_t[u_0] := u(t).$$

See Section 1.2.3 on page 6 concerning the square bracket notation.  $S_t$  is thus the solution operator of the diffusion problem. We list several interesting properties of this operator. Details and proofs can be found in [Weickert, 1998], but many of the properties are straight-forward consequences of the fact that the diffusion process is in divergence form and the diffusion tensor  $G(\nabla u_{\sigma})$  depends solely on  $\nabla u_{\sigma}$ . The following properties hold true for an arbitrary function  $v \in L^2(\Omega)$ , all  $x \in \mathbb{R}$  and all  $t, s \geq 0$  unless otherwise stated.

• Semigroup property

$$S_0 = 1,$$

$$S_{t+s} = S_t \circ S_s.$$

• Grey level shift invariance

$$S_t[0] = 0,$$

$$S_t[v+c] = S_t[v] + c, \text{ for } c \in \mathbb{R}.$$

• Reverse contrast invariance

$$S_t[-v] = -S_t[v]$$

#### 2 PDE Solvers in Quantized Image Processing

• Average grey level invariance

$$\mathcal{M}\big[S_t[v]\big] = \mathcal{M}[v] \,,$$

where  $\mathcal{M}: L^1(\Omega) \to L^1(\Omega)$  is the averaging operator defined by

$$\left(\mathcal{M}[v]\right)(x) := \frac{1}{|\Omega|} \int_{\Omega} v(y) \, dy.$$

• Translation invariance

$$(S_t \circ \tau_p)[v] = (\tau_p \circ S_t)[v],$$

for any translation  $(\tau_p[v])(x) := v(x+p)$  with supp  $\tau_p[v]$ , supp  $(\tau_p \circ S_t)[v] \subseteq \Omega$ .

• Isometry invariance

$$(S_t \circ R)[v] = (R \circ S_t)[v],$$

for any orthogonal transformation  $R \in \mathbb{R}^{2 \times 2}$  defined by (R[v])(x) := v(Rx) with supp R[v], supp  $(R \circ S_t)[v] \subseteq \Omega$ .

• Extremum principle

$$\operatorname{ess\,inf}_{\Omega} v \leq S_t[v(x)] \leq \operatorname{ess\,sup}_{\Omega} v$$

• Lyapunov functionals For  $v \in L^2(\Omega)$  and  $r \in C^2[\text{ess} \inf_{\Omega} v, \text{ess} \sup_{\Omega} v]$  with  $r'' \ge 0$ , the functional

$$\Phi[t,v] := \int_{\Omega} r\left(S_t[v(x)]\right) dx$$

is a Lyapunov functional:

$$\begin{split} \Phi[t,v] &\geq \Phi[0,\mathcal{M}[v]] \quad \forall t > 0, \\ \Phi[.,v] &\in C[0,\infty) \cap C^1(0,\infty), \\ \partial_t \Phi[t,v] &\leq 0 \quad \forall t > 0. \end{split}$$

If r'' > 0 on  $[ess \inf_{\Omega} v, ess \sup_{\Omega} v]$  then  $\Phi[t, v]$  is a strict Lyapunov functional:

$$\begin{split} \Phi[0,v] &= \Phi[0,\mathcal{M}[v]] &\iff v = \mathcal{M}[v] \text{ a.e. on } \Omega, \\ \partial_t \Phi[t,v] &= 0 \iff \Phi[t,v] = \Phi[0,\mathcal{M}[v]] \iff S_t[v] = \mathcal{M}[v] \text{ on } \Omega \quad \forall t > 0, \\ \Phi[0,v] &= \Phi[t,v] \text{ for } t > 0 \iff \begin{cases} v = \mathcal{M}[v] \text{ a.e. on } \Omega \text{ and} \\ S_s[v] = \mathcal{M}[v] \text{ on } \Omega, \forall s \in (0,t]. \end{cases} \end{split}$$

• Convergence

$$\lim_{t \to \infty} \|S_t[v] - \mathcal{M}[v]\|_p = 0 \text{ for } p \in [1, \infty)$$

We have listed these properties in such detail, because later we want to show that we can preserve many of this continuous properties in equivalent form in the discrete-quantized setting (Section 2.3.3 on page 49).

#### 2.1.1.3 Related Work

The non-linear diffusion models as we know them today were first introduced by a work of Perona and Malik [Perona and Malik, 1990]. Their model denoises images while retaining and enhancing edges. But analysis of the Perona-Malik model showed its mathematical ill-posedness [Kawohl and Kutev, 1998; Kichenassamy, 1997; You et al., 1996]. A regularized model [Catté et al., 1992] was derived, which can still preserve edges for an appropriately chosen regularization parameter. A thorough rigorous axiomatic theory of these methods under the term of scale-spaces was given in [Alvarez et al., 1993]. Different choices of the non-linearity and especially the use of the so called structure tensor for direction sensitive smoothing of images were presented in [Weickert, 1998].

#### 2.1.2 Segmentation - Level-Set Methods

The distribution of intensities in an image is usually perceived as a collection of objects by humans. Our visual system performs the task of segmenting the data into regions of certain characteristics. The fact that these regions often represent known objects simplifies the task. But even when meaning cannot be assigned, we still distinguish regions by certain features and sometimes even complete them in mind despite the absence of the corresponding information in the image. The human low level task of finding homogenous regions of some characteristic is coupled with the recognition of objects. Computer segmentation, however, seeks to perform the low-level task using appearance criteria only. The main difficulty lies in the appropriate encoding of the target objects' characteristics into these criteria. A very flexible method to account for these characteristics is the controlled expansion of a curve. Starting with a small circle such a curve is supposed to expand up to the borders of the segment in which it lies. Different object characteristics can be encoded by steering the expansion velocity of the curve with the local image values, their derivatives and the form of the curve. The level-set method is an implicit formulation of this expansion process, which naturally incorporates curve splitting and merging.

#### 2.1.2.1 Curve Evolution

We are given the original image  $p: \Omega \to \mathbb{R}$  on  $\Omega := [0, 1]^2$  and the initial curve  $C_0: [0, 1] \to \Omega$ . We represent this curve implicitly as the zero level-set  $\{x \in \Omega | \phi_0(x) = 0\}$  of a continuous function  $\phi_0: \Omega \to \mathbb{R}$  defined on the whole domain  $\Omega$ . Then we ask for a solution  $\phi: \mathbb{R}^+ \times \Omega \to \mathbb{R}$  to the *level-set equation*

(2.5)

$$\partial_t \phi + f^{\sigma}[\phi] \cdot \nabla \phi = 0 , \quad \text{in } \mathbb{R}^+ \times \Omega , \phi(0) = \phi_0 , \quad \text{on } \Omega ,$$

where  $f^{\sigma}[\phi]$  is the velocity field which drives the evolution of the level-set function  $\phi$ . In case of a complex velocity field with varying directions on the boundary it is not obvious how to

define boundary conditions for  $\phi$ . Following [Sethian, 1999] we impose a mirror boundary condition for  $\phi$  on  $\mathbb{R}^+ \times \partial \Omega$ . The velocity field is usually composed of three different forces

$$f^{\sigma}[\phi] = f_{g}^{\sigma} \frac{\nabla \phi}{\|\nabla \phi\|} + f_{\kappa}[\phi] \frac{\nabla \phi}{\|\nabla \phi\|} + f_{V},$$

where  $f_g^{\sigma}$  and  $f_{\kappa}[\phi]$  are forces in the normal direction of the level-sets and  $f_V$  is independent thereof. The square brackets denote operators, see Section 1.2.3 on page 6. The forces have different impact on the evolution:

• External forces  $f_g^{\sigma}(t,x) = c(t,x) + g_1(p(x)) + g_2(\|\nabla p_{\sigma}(x)\|).$

The first term c(t, x) can prescribe a default expansion speed and will usually be simply a constant value. By using a characteristic function  $\chi_R$  it can also favor the expansion in an a-priori known region of interest R. The other terms take into account local information of the image p and may take the following form:

(2.6)

$$g_1(y) := \mathcal{G}_{\mu,c_{g_1}}(y) = (2\pi c_{g_1}^2)^{-\frac{1}{2}} \exp\left(-\frac{1}{2}\frac{(y-\mu)^2}{c_{g_1}^2}\right),$$

$$g_2(y) := \mathcal{P}_{c_{g_2}}(y) = \frac{1}{1+c_{g_2}y^2},$$

with the similar use of the Gaussian function  $\mathcal{G}_{\mu,c_{g_1}}$  and the Perona-Malik function  $\mathcal{P}_{c_{g_2}}$ as for the diffusion processes in Section 2.1.1.1 on page 15. The effect is to forward expansion in areas with intensities similar to  $\mu$  and small mollified gradients. The mollification controlled by  $\sigma$  prevents too high sensitivity of the gradient to noise. Such evolution produces segments with smoothly distributed intensity around  $\mu$ . Depending on the choice of  $c_{g_1}$  and  $c_{g_2}$  the similarity to  $\mu$  or the smoothness of the segment is more relevant.

• Curvature  $f_{\kappa}[\phi](t,x) = -c_{\kappa}\kappa[\phi](t,x).$

The curvature  $\kappa$  in two dimensions is given as

$$\kappa[\phi] := \nabla \cdot \frac{\nabla \phi}{\|\nabla \phi\|} = \frac{\phi_{xx} \phi_y^2 - 2\phi_x \phi_y \phi_{xy} + \phi_{yy} \phi_x^2}{(\phi_x^2 + \phi_y^2)^{3/2}},$$

where subscripts indicate partial derivatives here. The inclusion of this term will hamper the formation of high curvature bends in the level-sets. This is especially useful in preventing the propagation front from expanding through a narrow hole in an almost complete segment border. By this one wants to mimic to a certain degree the human ability for form completion. The general effect is an evolution of smoother level-sets.

• Velocity field  $f_V(t, x) = V(t, x)$ .

Level-set methods are often used in the tracking of phase boundaries between different materials or material states. In these applications the whole system is usually subjected to forces which act on the interface independent of its form. Therefore, the possibility of an external velocity field interfering with the evolution is given. But also in the case

of segmentation such a field may be useful to penalize the deviation of the segment from an a-priori given default form. This feature could also help to complete a segment in areas where the boundary information is missing in the data.

The solution  $\phi : \mathbb{R}^+ \times \Omega \to \mathbb{R}$  of the problem represents a family of successively evolved levelsets  $L(t,c) := \{x \in \mathbb{R}^2 | \phi(t,x) = c\}, c \in \mathbb{R}$ . The curves  $L(t,0), t \ge 0$  describe the evolution of our initial curve  $C_0 = L(0,0)$ . In the asymptotic state  $t \to \infty$  the curve L(t,0) converges to an equilibrium of forces or expands over the borders of the image. For applications, however, we are interested only in a finite and preferably short evolution time T, such that the process is stopped as soon as the changes in the level-sets become very small.

#### 2.1.2.2 Hamilton-Jacobi Equation

By introducing the Hamilton function  $H(u) := f_p ||u|| + f_V \cdot u$  we may reformulate the level-set equation in the form of a Hamilton-Jacobi equation

$$\partial_t \phi + H(\nabla \phi) = c_{\kappa} \kappa[\phi] \| \nabla \phi \|.$$

with a parabolic viscosity term on the right hand side. Further setting  $u := \nabla \phi$  and differentiating the above equation leads to the hyperbolic conservation law:

(2.7)

$$\partial_t u + \nabla(H(u)) = c_\kappa \nabla\left(\|u\|\nabla\frac{u}{\|u\|}\right).$$

Because of their importance in physics conservation laws and their numerical implementations have been studied thoroughly [Corrias et al., 1995]. Therefore, this alternative perspective on the level-set equation helps us later to find the appropriate discretization.

#### 2.1.2.3 Related Work

Active contour models which describe the evolution of a initial curve driven by the underlying image, external data and curve form have become a very popular tool in image segmentation [Osher and Sethian, 1988]. The development started with explicitly parameterized curve representations. But the key disadvantage of this method is a topological constraint: the curve cannot split to approximate boundaries of not simply connected segments. Such problems have been solved by introducing implicit models [Caselles et al., 1993; Malladi et al., 1995], in which the initial curve is interpreted as the zero level-set of a function defined on the whole domain. The evolution of this function is controlled by a PDE [Sethian, 1999]. Sensitivity of the process to initialization has been later reduced by an appropriate choice of driving forces [Xu and Prince, 1998]. Furthermore a general variational framework for Mumford-Shah and Geman type functionals [Geman et al., 1990; Mumford and Shah, 1985] has been introduced [Hewer et al., 1998], where edge boundaries are represented by a discontinuous function, yielded by the minimization of an energy functional.

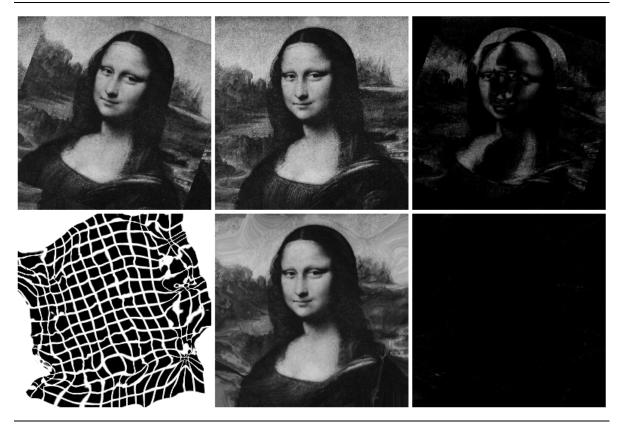

## 2.1.3 Registration - Energy Gradient Flows

Images often come as a series of exposures of the same object from different times or perspectives, sometimes even acquired by different imaging technologies. The series are used for the analysis of temporal changes or the overall structure of the object. The analysis requires an information correlation between two images. A correlation is ideally given by a deformation of the images which matches the object representation of the first image onto that of the second. The quality of the deformation depends on the definition of optimal matching criteria.

For a clearly arranged configuration the human visual system quickly suggest an appropriate deformation. But without any semantic knowledge about the content of the images in the computer, the matching criteria must rely solely on the image intensities and their geometric distribution and therefore often do not suffice to pinpoint the optimal deformation, especially when the images contain a diffuse distribution of intensities; then we are faced with a multitude of possible solutions and must introduce some reasonable assumptions on the deformation to distinguish among them. Energy gradient flows allow a very flexible way to define and control these additional assumptions which are crucial in the search for a reasonable image correlation.

#### 2.1.3.1 Energy Model

Given two images, a template and a reference  $T, R : \Omega \to \mathbb{R}, \Omega \subset \mathbb{R}^2$ , we look for a deformation  $\phi : \Omega \to \Omega$  which maps the intensities of T via  $\phi$  to the intensities of R such that

$$T \circ \phi \approx R$$

.

Since  $\phi$  is usually small in comparison to  $|\Omega|$  it can be suitably expressed as  $\phi = 1 + u$ , with a displacement function u. The displacement u is sought as the minimum of the energy

$$E[u] = \frac{1}{2} \int_{\Omega} |T \circ (\mathbf{1} + u) - R|^2$$

The square brackets are used for operators, see Section 1.2.3 on page 6.

A minimizer u in some Banach space  $\mathcal{V}$  is characterized by the condition

$$\int_{\Omega} E'[u] \cdot \theta = 0$$

for all  $\theta \in [C_0^{\infty}(\Omega)]^2$ , with the  $L^2$ -representation of E'

$$E'[u] = (T \circ (\mathbb{1} + u) - R)\nabla T \circ (\mathbb{1} + u),$$

if we assume T to be smoothly differentiable. This gradient may be used as the descent direction towards a minimum in a gradient descent method. But there may be many minima since any displacements within a level-set of T do not change the energy. To guarantee that the

gradient descent converges to a unique solution, we have therefore to exclude solutions which contain irregular mappings within the level-sets of T by applying a regularization technique. The descent along the gradient will be regularized by  $A(\sigma)^{-1}$ , with

$$A(\sigma) = 1 - \frac{\sigma^2}{2} \Delta, \ \sigma \in \mathbb{R}^+ \,.$$

Then the regularized gradient flow

(2.8)

$$\begin{aligned} \partial_t u &= -A(\sigma)^{-1} E'[u], \quad \text{in } \mathbb{R}^+ \times \Omega, \\ u(0) &= u_0, \quad \text{on } \Omega, \end{aligned}$$

has a unique solution u with  $u(t) \in \mathcal{V}$  for some function space  $\mathcal{V}$  (Theorem 3.1 [Clarenz et al., 2002]). In the implementation the regularization with  $A(\sigma)^{-1}$  can be quickly realized by a multi-grid cycle with few smoothing steps, because we do not require the exact solution but rather the smoothing properties.

#### 2.1.3.2 Multi-Scale Hierarchy

Since the energy E is non-convex the gradient descent path may easily get trapped in local minima instead of finding the global minimum of E. Therefore, a continuous annealing method is used by defining a multi-scale of image pairs

(2.9)

$$T_{\epsilon} := S(\epsilon)T,$$

$$R_{\epsilon} := S(\epsilon)R,$$

for  $\epsilon \ge 0$  with a filter operator S. The choice  $S(\epsilon) = A(\epsilon)^{-1}$  corresponds again to a Gaussian filtering. The energy

$$E_{\epsilon}[u] = \frac{1}{2} \int_{\Omega} |T_{\epsilon} \circ (\mathbb{1} + u) - R_{\epsilon}|^2$$

induces the corresponding gradient flow on scale  $\epsilon$ , which has the solution  $u_{\epsilon}$ .

For the annealing process we choose an exponentially decreasing series of scales  $(\epsilon_k)_{k=0,...,K}$ ,  $K \in \mathbb{N}$  with  $\epsilon_0 = 0$  and use the approximate solution of the gradient flow problem from a coarser scale  $\epsilon_k$  at a sufficiently large time  $t_{\epsilon_k}$  as the initialization for the gradient flow problem on a finer scale  $\epsilon_{k-1}$ , i.e. we perform:

$$u_{\epsilon_K}(0) := 0,$$

$$u_{\epsilon_{k-1}}(0) := u_{\epsilon_k}(t_{\epsilon_k}),$$

for i = K - 1, ..., 1 until the final solution  $u_{\epsilon_0}(t_{\epsilon_0})$  on the finest scale  $\epsilon_0$  is reached. In the implementation the multi-scales can be efficiently encoded in a multi-grid hierarchy.

#### 2.1.3.3 Related Work

If we measure image coherence by the energy  $E[u] = \frac{1}{2} \int_{\Omega} |T \circ \phi - R|^2$ , where T, R are the intensity maps of the images and  $\phi$  the deformation, then the minimization problem is ill-posed, because arbitrary deformations within the level-sets of T do not change the energy. Therefore, many regularizations of the registration problem have been discussed in the literature [Christensen et al., 1997; Davatzikos et al., 1996; Grenander and Miller, 1998; Maes et al., 1997; Thirion, 1998]. The registration approach given above was introduced in [Clarenz et al., 2002]. But the ideas are similar to the iterative Tikhonov regularization methods [Hanke and Groetsch, 1998], fast multi-grid smoothers [Henn and Witsch, 2001] and multi-scale use for large displacements [Alvarez et al., 2000] presented previously.

# 2.2 Discretization - Quantization

In this section we develop a common setting for the discretization and quantization of the continuous models. The similar treatment offers advantages for the analysis of the discrete algorithms and already pays attention to hardware issues by explicitly exposing the inherent parallelism of the algorithms. The similar structure of the algorithms is also important for the reuse of the same architecture for different image processing tasks.

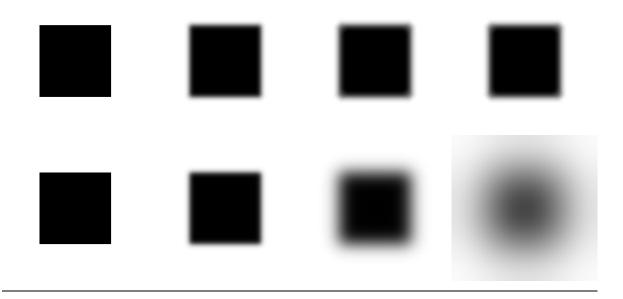

Concerning the quantization we give a short overview of different number formats, their shortcomings with respect to accuracy in computations and attempts to remedy these problems. Then we concentrate on methods which help to conserve the qualitative behavior of the continuous models even under quantization that is so coarse that it defeats the direct methods of error enclosure or statistical control. Error analysis of this methods shows also the limitations of this approach.

### 2.2.1 Discrete Operators

Although the introduced models for denoising, segmentation and registration are fairly different they have the common form:

(2.10)

$$\partial_t u + \mathcal{F}[\mathcal{C}^p_{\sigma}[u], u] = 0 , \quad \text{in } \mathbb{R}^+ \times \Omega , u(0) = u_0 , \quad \text{on } \Omega ,$$

with an additional condition on  $\mathbb{R}^+ \times \partial \Omega$  for the *generic diffusion* model and the *level-set equa*tion which involve spatial derivatives of the unknown. Here,  $\mathcal{C}^p_{\sigma}[u]$  and  $\mathcal{F}[u, v]$  are operators

|        | problem      | equation           | $\mathcal{C}^p_{\sigma}[u]$ | $\mathcal{F}[u,v]$      |

|--------|--------------|--------------------|-----------------------------|-------------------------|

| (2.11) | denoising    | Eq. 2.1 on page 16 | $G(\nabla u_{\sigma})$      | $-{\rm div}(u\nabla v)$ |

| (2.11) | segmentation | Eq. 2.5 on page 19 | $f^{\sigma}[u]$             | $u \cdot v$             |

|        | registration | Eq. 2.8 on page 23 | $A(\sigma)^{-1}E'[u]$       | u                       |

on the Banach space  $\mathcal{V}$ . For the discussed problems they read:

The non-linear operator  $C^p_{\sigma}[u]$  serves as a local *classifier*, i.e. the function u is locally classified with respect to the desired evolution. The indices p and  $\sigma$  indicate that the classifier may depend on additional input data p and regularization parameters  $\sigma$ , which control the data sensitivity of the process. The result of the operator can be considered as a weight function, which determines the magnitude of impact of the regions of u at the current time t on the evolution of u. The operator  $\mathcal{F}[u, v]$  performs the application of these weights. It may still involve spatial derivatives, but has to be linear in u and either also linear in v or independent of v.

The unified PDE scheme for the problems (Eq. 2.10 on the facing page) helps us to define a common discretization approach.

#### 2.2.1.1 Time Discretization

We use explicit and implicit schemes for time discretization. The simple explicit Euler gives:

(2.12)

$$u^{n+1} = u^n - \tau^n \cdot \mathcal{F}[\mathcal{C}^p_{\sigma}[u^n], u^n]$$

This schemes has the advantage of fast execution and allows good control of quantization effects but is quite restricted in the time-step width  $\tau^n$ . The *Courant-Friedrichs-Levy (CFL)* condition requires that

(2.13)

$$\|\tau^n \cdot \mathcal{F}[\mathcal{C}^p_{\sigma}[u^n], u^n]\|_{\infty} < h,$$

if h is the element grid size in the spatial discretization, i.e. information is prohibited to cross a whole grid cell in one time-step. We will use the explicit discretization for the level-set method in the segmentation problem and the gradient descent in the registration problem.

The fully implicit Euler scheme

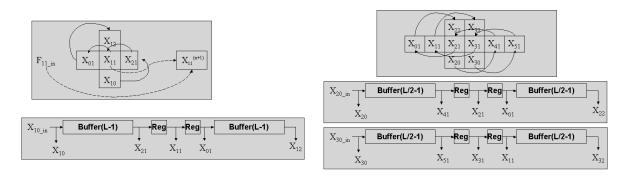

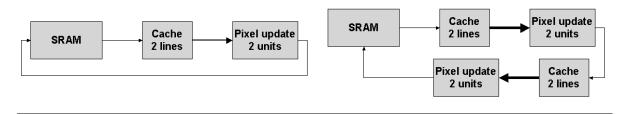

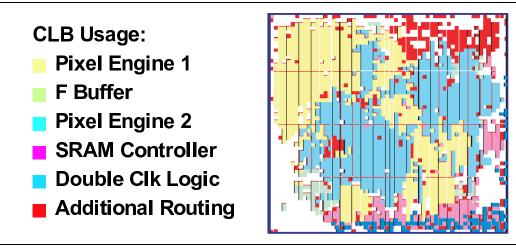

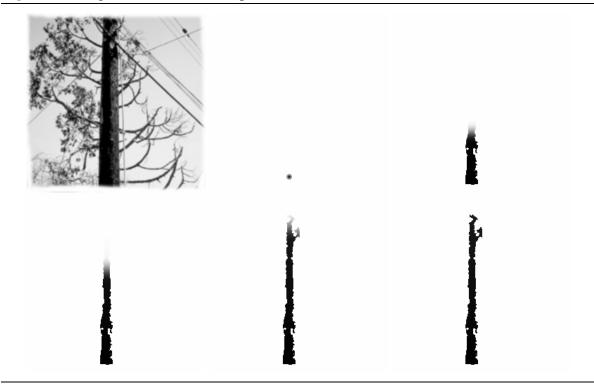

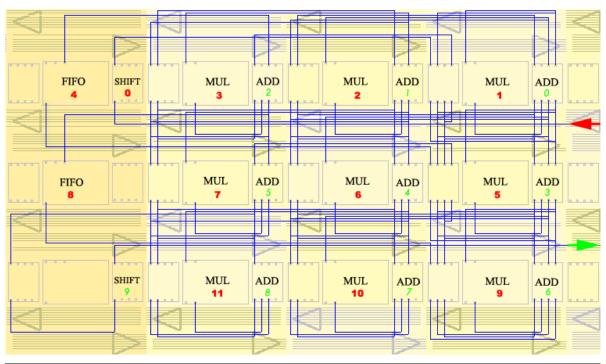

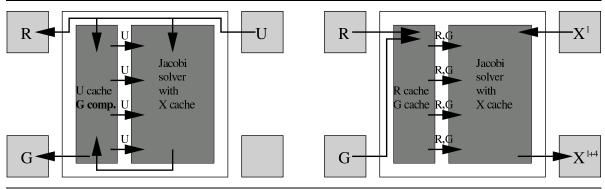

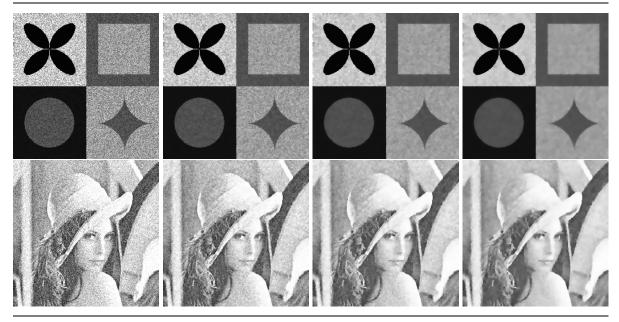

(2.14)